No Space Wasted: Embedding Capacitors into Interposers to Increase Miniaturization

Press Releasesおすすめ

Dr. Takayuki Ohba (Heterogeneous and Functional Integration Unit)

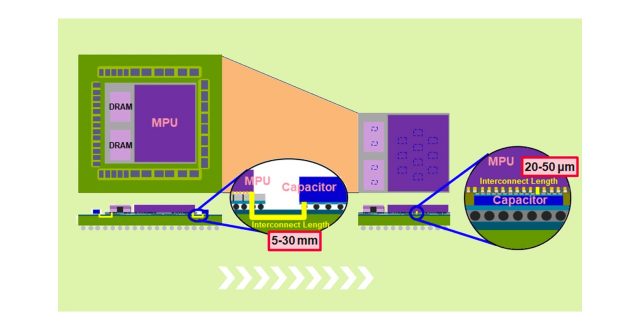

Scientists at Tokyo Institute of Technology develop a 3D functional interposer—the interface between a chip and the package substrate—containing an embedded capacitor. This compact design saves a lot of package area and greatly reduces the wiring length between the chip’s terminals and the capacitor, allowing for less noise and power consumption. Their approach paves the way to new semiconductor package structures with greater miniaturization.

Title of original paper: “Miniaturized 3D Functional Interposer Using Bumpless Chip-on-Wafer (COW) Integration with Capacitors”

For details, click here!

Please send any inquiries about WRHI to us.